低壓差線性穩(wěn)壓器(LDO)是模擬集成電路中廣泛使用的電源管理模塊,其設(shè)計過程高度依賴專業(yè)軟件開發(fā)工具。本文將系統(tǒng)闡述LDO模擬集成電路設(shè)計中涉及的軟件開發(fā)流程。

1. 設(shè)計規(guī)范與架構(gòu)規(guī)劃階段

在設(shè)計初期,工程師需使用系統(tǒng)級設(shè)計工具(如MATLAB/Simulink)建立LDO的架構(gòu)模型。通過行為級仿真確定關(guān)鍵參數(shù):壓差電壓、負(fù)載調(diào)整率、線性調(diào)整率、靜態(tài)電流等。此階段需編寫配置腳本定義工作條件,并生成初步的設(shè)計規(guī)范文檔。

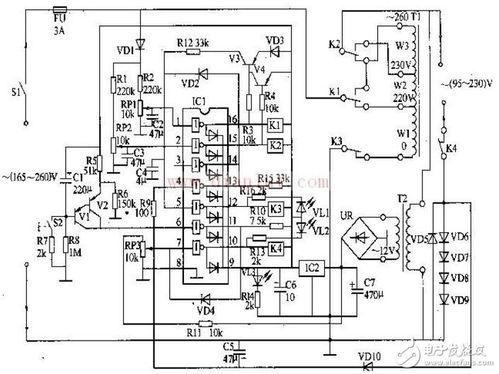

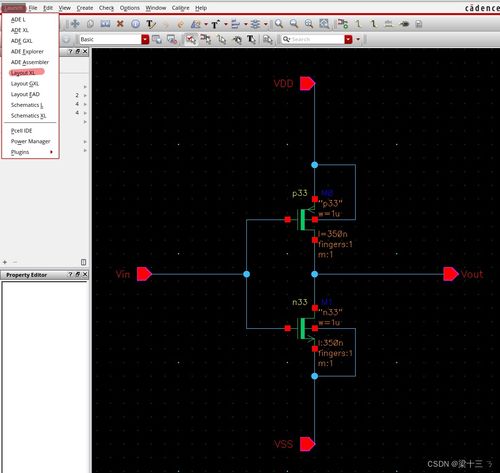

2. 電路設(shè)計與仿真驗證

進(jìn)入電路級設(shè)計后,工程師采用專業(yè)EDA工具鏈:

- 使用Cadence Virtuoso或Synopsys Custom Compiler進(jìn)行原理圖設(shè)計

- 通過Spectre、HSPICE等仿真器進(jìn)行DC、AC、瞬態(tài)和穩(wěn)定性分析

- 利用ADE Explorer/Assembler設(shè)置仿真參數(shù)和蒙特卡洛分析

- 編寫Ocean/VerilogA腳本實現(xiàn)自動化仿真流程

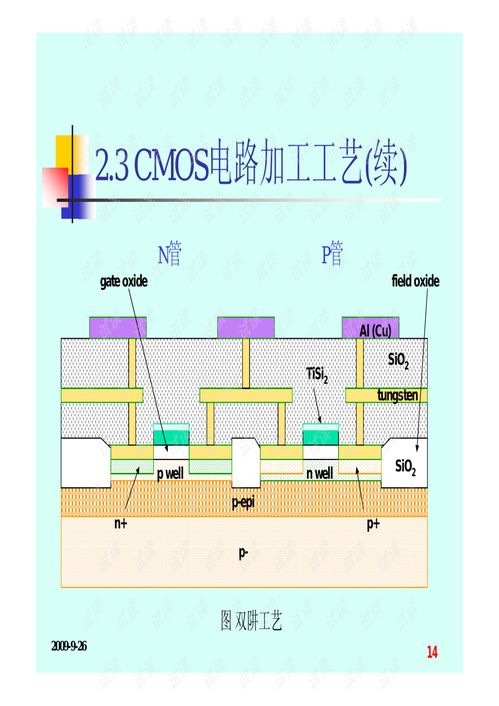

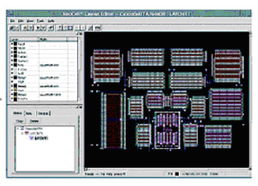

3. 版圖設(shè)計與驗證

在物理實現(xiàn)階段:

- 使用Virtuoso Layout Suite進(jìn)行版圖繪制

- 運(yùn)行Calibre或Assura進(jìn)行DRC/LVS驗證

- 通過RC提取工具生成寄生參數(shù)文件

- 進(jìn)行后仿真驗證性能指標(biāo)

4. 芯片測試與數(shù)據(jù)采集

流片后使用LabVIEW或Python開發(fā)測試程序:

- 控制自動測試設(shè)備(ATE)執(zhí)行特性測試

- 采集關(guān)鍵參數(shù)數(shù)據(jù)并生成測試報告

- 開發(fā)數(shù)據(jù)分析腳本進(jìn)行性能評估

5. 設(shè)計優(yōu)化與迭代

基于測試結(jié)果,工程師需要:

- 使用SKILL語言或Python開發(fā)設(shè)計優(yōu)化算法

- 建立設(shè)計-仿真-驗證的自動化閉環(huán)流程

- 維護(hù)版本控制系統(tǒng)(如Git)管理設(shè)計文件

現(xiàn)代LDO設(shè)計已形成完整的軟件支撐體系,從系統(tǒng)建模到物理實現(xiàn),再到測試驗證,每個環(huán)節(jié)都依賴專業(yè)的軟件開發(fā)。熟練掌握EDA工具鏈和腳本開發(fā)能力,已成為模擬集成電路設(shè)計師的核心競爭力。隨著人工智能技術(shù)的發(fā)展,基于機(jī)器學(xué)習(xí)的自動化設(shè)計方法正在逐步應(yīng)用于LDO優(yōu)化設(shè)計中,這將進(jìn)一步推動設(shè)計效率和性能的提升。